画像変形処理回路を開発 ―小型FPGAに実装できる画像変形回路―

様々な製造現場では、ライン上の製品をカメラで撮影し、良品検査を行なう自動検査システムが使用されています。ライン上の製品は常に規則正しい位置にあるとは限らず、位置ズレが発生することがあります。このため、検査を行なう前に撮影した画像を変形処理することで、ズレを解消したいというニーズがあります。このような処理は高価な専用LSI(大規模集積回路)で行なわれるためコスト面が課題となっていました。そこで、工業試験場では、近年、回路規模、動作速度面で実用的なデジタル回路を構築できるようになった安価な小型FPGA(書換え可能な大規模集積回路)を使用して、高速に画像の移動、拡大縮小、回転の処理が可能な回路の開発に取り組みました。

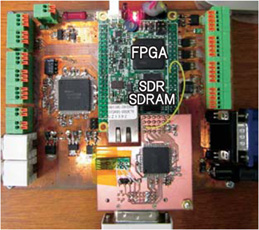

開発した回路は、120万ゲート規模の小型FPGAと、配線に特殊な技術を必要としないSDR-SDRAM(低速度動作メモリ)で構成され(図1)、動画であれば640×480ドットのモノクロ画像を毎秒60枚、静止画であれば2048×2048ドットのモノクロ画像を毎秒5枚処理することができます(図2)。今回開発した変形処理回路の規模は、120万ゲートの15%程度に収まりました。

開発した回路は検査システムの位置ズレ修正部に使用することが可能です。今後、本開発を含め、県内企業へFPGAに関する技術支援を行っていきます。

|

|

| 図1 試作回路 | 図2 変形例 |

担当:電子情報部 田村 陽一(たむら よういち)

専門:電子回路

一言:小型FPGAでも十分に画像を扱えます。